Intel teams up with Glasgow to design future nanoscale memory chips

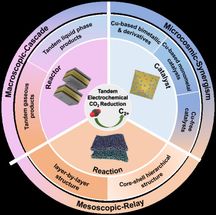

A European taskforce has been set up to investigate how to design the next generation of tera-scale computer memory systems - with Glasgow playing a key role. Within the next decade microchips are expected to incorporate billions of transistors – the tiny on-off switches that enable circuits to process and store data – creating ultra-powerful computer systems that can process trillions of bytes (terabytes) of data per second.

However, as transistors get smaller, so tiny variations within their structures affect their performance and thus the reliability of the whole microchip. It is a problem which presents a huge barrier to the continued scaling of microchips and the development of ever-more powerful computers. In order to overcome this obstacle the European Commission (EC) has established a taskforce to come up with new ways of designing future microchip memories which take into account the variability and unreliability of nano-scale transistors.

The ‘Tera-scale Reliable Adaptive Memory Systems’ (TRAMS) consortium includes: Intel Corporation Iberia, Interuniversitair Micro-Elektronica Centrium vzw, the University of Glasgow, and the Universitat Politecnica de Catalunya, and is financed through the EU’s Framework Programme 7 (FP7) science research fund.

Professor Asen Asenov, of the Department of Electronic and Electrical Engineering is leading the University of Glasgow’s involvement at the heart of the project. He is a world-leading authority on the variability of Complementary Metal-Oxide Semiconductors (CMOS) transistors and microchips.

He said: “Tera-scale computing will transform the power, performance and functionality of personal computers, phones and other electronic devices as well as large computing facilities such as data centres.

“However, if we are to continue to shrink the size of transistors in order to develop such powerful circuits, we need fundamentally new approaches to circuit and system design that can take account of the variability within transistors.

“We hope this project will result in new chip design paradigms for building reliable memory systems out of unreliable nano-scale components cheaply and effectively, heralding the era of tera-scale computing.”

Central to the project is simulation software developed by Prof Asenov in an earlier £5.3m Engineering and Physical Sciences Research Council eScience pilot project called NanoCMOS.

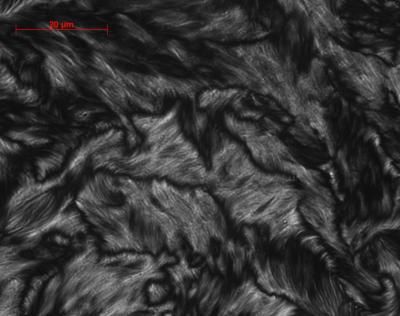

The NanoCMOS simulations use grid computing, which utilises the processor power of thousands of linked computers, to simulate how hundreds of thousands of transistors, each with their own individual characterstics, will function within a circuit.

Prof Asenov and the University of Glasgow is setting up a company called Gold Standard Simulations to exploit this technology which will be critical to the work of the TRAMS project, with all device design and simulation work being conducted at Glasgow.

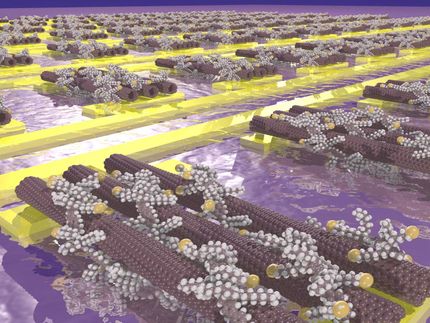

In investigating design possibilities for future microchips, the team will focus on future generation of CMOS microchip technologies – which comprise transistors less than 16 nanometres in size (by comparison a human hair is around 100,000 nanometres wide). The transistors will be design and simulated exclusively by Glasgow.

The TRAMS consortium will also consider what are known as ‘Beyond CMOS’ technologies; nanowire transistors, quantum devices, carbon nanotubes and molecular electronics, which are expected to be as small as five nanometres.

The project is expected to last three years.

Most read news

Topics

Organizations

Other news from the department science

Get the chemical industry in your inbox

By submitting this form you agree that LUMITOS AG will send you the newsletter(s) selected above by email. Your data will not be passed on to third parties. Your data will be stored and processed in accordance with our data protection regulations. LUMITOS may contact you by email for the purpose of advertising or market and opinion surveys. You can revoke your consent at any time without giving reasons to LUMITOS AG, Ernst-Augustin-Str. 2, 12489 Berlin, Germany or by e-mail at revoke@lumitos.com with effect for the future. In addition, each email contains a link to unsubscribe from the corresponding newsletter.